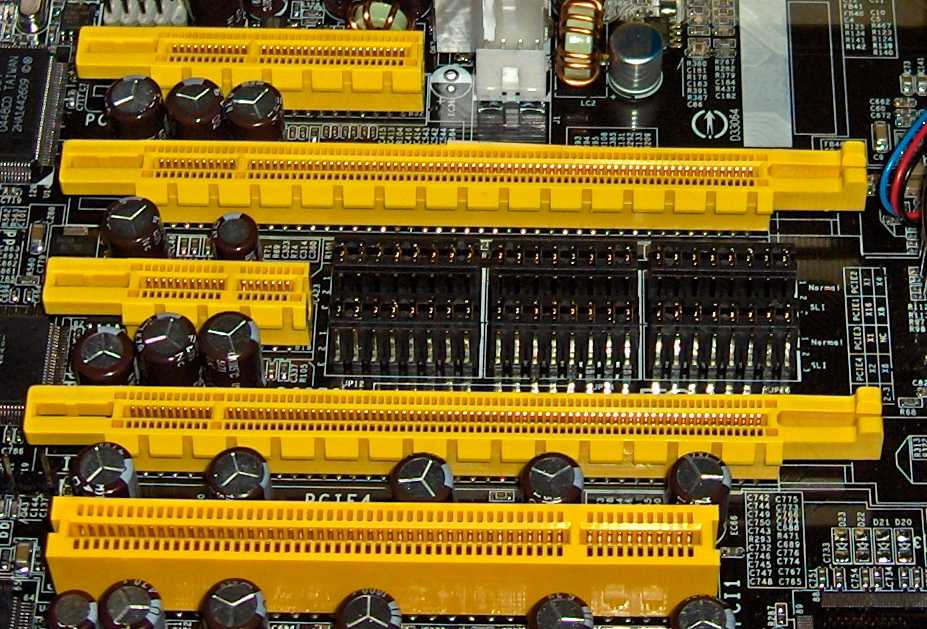

PCIe 5.0 Model Development and Testing using C++, LISA

In this project, as a team member of FVP Modeling Team at ARM, I was involved in the following work as follows:

* Implementation of Various PCIe Model Features such as Type0 Configuration, Type1 Configuration, various register set functionalities and capabilities.

* Involvement in creating a JSON Parser program to create PCIe Hierarchy at run-time, by passing the JSON file as a command-line parameter to the model.

* Involvement in implementation device-specific functionalities for Exerciser, SMMUv3TestEngine, etc.

* Testing each and every feature of the PCIe Model using Google Test Unit Test and UEFI based System Test.

* Feature Tested: Seamless Config, Memory Transaction, MSI, Legacy Interrupt, Error Forwarding, etc., Access Control Services, Transaction routing, etc.

* Setup a Nightly Build CI to run SBSA(System Architecture), PCIe System Test, and Unit Test on a daily basis and mail the detailed analysis of the tests to all members of FVP Modeling Team, with errors, test-failures, last day commits for different repositories used.

* Used bash shell scripting, python scripting, Perl scripting to automate testing, setting up an environment for PCIe Model, etc.

* Handling Various PCIe Model Bugs and Test Failures from Internal and external partners.

* Used debuggers like GDB, Valgrind, ARM-Based Exception Handlers, etc. - Worked with LISA tool as a replacement for SystemC Interface.

22 Dec 2019