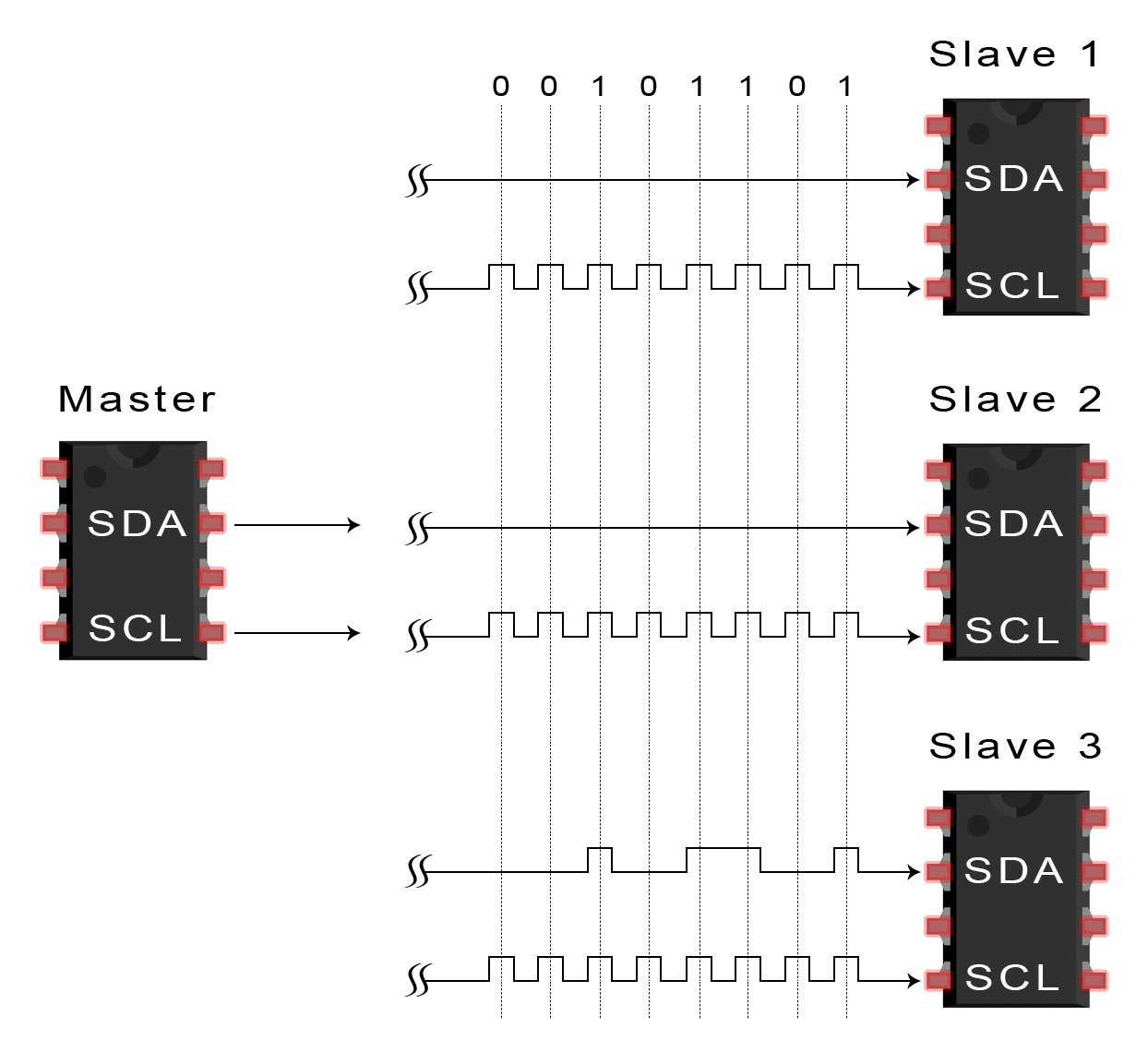

I2C Front End Design using SystemC

Implemented I2C Master and I2C Slave in SystemC at a signal level as per I2C protocol.

* I2C Master reads from data bytes and address via ports and fill data into Master FIFO and address into a signal.

* Master generates the clock SCL.

* Master thread sends START bit,7/10 bit Slave address, and control bit for reading/writing operation.

* After receiving acknowledgment from the slave via SDA, data transfers start bit by bit through the SDA line.

* Slave synchronizes after reading START bit.

* Slave reads or writes data from/ into the SDA synchronized with SCL.

* De-serializers statements are used to convert these bits into a byte and storing the bytes either in Master FIFO or Slave FIFO.

* For verifying the output, the waveform was generated and GTK-wave was used to check the waveform.

* Also wrote the Testbench module compares the Master FIFO and Slave FIFO and verifies the result of I2C transfer.

15 Jan 2019